Thermal Management

The Thermal Management Subgroup works mainly on development of the design and implementation of efficient heat dissipation solutions for electronic devices, including efficient thermal simulation methods for 3D IC systems, microfluidic cooling simulation design/fabrication, processing/long-run reliability study of embedded microfluidic cooling in advanced packaging, etc. The members consist of Deyin Zheng (Ph.D.), Yuchi Yang (Ph.D. candidate), Motong Li (Ph.D. candidate), Jianyu Du (Ph.D. student), Yudong Yang (Ph.D. student), Tiebin Zhang (Master student), Siqi Ding (Master student), Peijue Lyu (Master student). By now, they have achieved:

1. Full-Chip-Scale Thermal Simulation Method for 3D IC

An equivalent anisotropic thermal conductivity model was proposed to calculate the system-level temperature distribution. It can greatly simplify the calculation by reducing the geometric size difference to less than one order of magnitude. The accuracy of the simplification was guaranteed by introducing the modified equivalent method and the thermal wire effective coefficient which represent a consideration of heat flux distribution.

A finite element numerical simulation method based on equivalent thermal conductivity model is developed, which holds advantages of high accuracy achieved by finite element method and low computational consumption by introducing the equivalent thermal conductivity. The process includes data structure extracting, geometry simplification, numerical model establishment, and FE calculation. System level thermal information including temperature distribution can be obtained by post-

analysis.

2. Embedded microfluidic cooling for large-area high-power chips

For high-power chip application such as servers, high-performance computing (HPC), and data centers, a compact embedded microfluidic cooling chip was designed, fabricated. A double H type manifold channel was innovatively proposed for fluid distribution to improve the volume flow rate of working fluid. This channel structure design is compatible with the current mainstream flip-chip packaging. Using a simulated heat source with a size of 20 mm × 20 mm, an effective cooling of 417 W was achieved under the operating conditions of a pump pressure drop of 35.0 kPa and a flow rate of 612 ml/min. The maximum temperature rise and the average temperature rise on the chip surface measured by the on-chip platinum temperature sensor are only 34.7 K and 22.2 K.

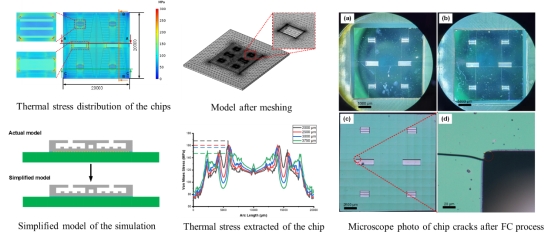

3. Thermal stress analysis of large area chip with embedded microchannels

To ensure the reliability of large area chip with embedded microchannels during the FC process. By building a simplified model to study the mechanical failure induced by the shapes of the inlets and the outlets of the chips. Thermal stress of the inlets and outlets in different shapes and sizes was studied. The thermal stress distribution is significantly improved by changing the curvature of the shapes of the inlets and the outlets. A more uniform stress distribution can be obtained after designing the inlets and the outlets as circles or ellipses, and the maximal thermal stress will decrease more than 70 %.